с выхода РЕ0 на вход РQ3. Одновременно выполняется сдвиг множителя в RQ на один разряд вправо.

На ( $n+1$ )-м такте знаковый разряд множителя находится нашине 2 младшей процессорной секции. В это время необходимо подать микрокоманду последнего такта умножения в дополнительном коде (коррекция результата).

## РАБОТА 5. МИКРОПРОГРАММЫ ВЫПОЛНЕНИЯ ОПЕРАЦИЙ ДЕЛЕНИЯ

Цель работы: приобретение практических навыков составления микропрограмм при выполнении операций деления.

### Индивидуальное задание

1. Разработать микропрограмму выполнения операции деления 8-разрядных дробных чисел по алгоритму,енному в табл. 12. Выполнить контрольный пример над операндами, представленными в табл. 13. Разрядность процессора принять равной разрядности исходных операндов. Блок микропрограммного управления выполнить с использованием регистра состояния для хранения признаков.

2. Оформить микропрограмму деления в виде подпрограммы. Обеспечить задание исходных операндов и вызов подпрограммы из основной программы.

## РАБОТА 6. РАЗРАБОТКА СТРУКТУРНОЙ СХЕМЫ И МИКРОПРОГРАММЫ ВЫПОЛНЕНИЯ ОПЕРАЦИИ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ С ПЛАВАЮЩЕЙ ЗАПЯТОЙ

Цель работы: изучение алгоритмов операций сложения и вычитания с плавающей запятой и способов выполнения этих операций в секционных микропроцессорах 1804.

### Индивидуальное задание

Рассмотреть все этапы выполнения заданной операции с плавающей запятой (сложения или вычитания операндов) с учетом знаков операндов. Можно выделить в общем случае три таких этапа: вырав-

ТАБЛИЦА 12

| $d_1$ | $d_2$ | АЛГОРИТМ ДЕЛЕНИЯ             |

|-------|-------|------------------------------|

| 0     | 0     | $a_1 [ СВО , L_1(0) ]$       |

| 0     | 1     | $a_2 [ БВО , L_1(0) ]$       |

| 1     | 0     | $\delta_1 [ СВО , R_1(ДТ) ]$ |

| 1     | 1     | $\delta_2 [ БВО , R_1(ДТ) ]$ |

| $d_3$ |       | ПРЕДСТАВЛЕНИЕ ОПЕРАНДОВ      |

| 0     |       | ДОПОЛНИТЕЛЬНЫЙ КОД           |

| 1     |       | ПРЯМОЙ КОД                   |

| $d_4$ |       | ОПЕРАЦИОННАЯ ЧАСТЬ           |

| 0     |       | K1804BC2                     |

| 1     |       | K1804BC1                     |

ТАБЛИЦА 13

| $d_5$ | $d_6$ | ДМ  | ДТ  | $d_7$ | $d_8$ | ДМ  | ДТ |

|-------|-------|-----|-----|-------|-------|-----|----|

| 0     | 0     | R11 | R15 | 0     | 0     | -76 | -6 |

| 0     | 1     | R2  | RQ  | 0     | 1     | +58 | -7 |

| 1     | 0     | R3  | R4  | 1     | 0     | -64 | +8 |

| 1     | 1     | RQ  | R5  | 1     | 1     | 83  | -9 |

нивание порядков, сложение (вычитание) мантисс и нормализация результата. Заключительный этап предусматривает выбор структуры аппаратной части микропроцессора (МП), построение микропрограмм, интерпретирующих выбранный алгоритм на фиксированной выбранной структуре аппаратной части МП, расчет быстродействия МП.

### Методические указания

При выполнении задания следует принять, что исходные данные (нормализованные или равные нулю операнды) к моменту выполнения операции занесены во внутренние РОН МП в следующем порядке: модуль мантиссы первого операнда - в РОН R0 (0000), порядок первого операнда в РОН R1 (0001), знак первого операнда - в старшем разряде РОН R2 (0010), модуль мантиссы второго операнда - в РОН R3 (0011), порядок второго операнда - в РОН R4 (0100), знак второго операнда - в старшем разряде РОН R5 (0101). Модуль мантиссы результата должен быть записан в РОН R0, порядок результата - в РОН R1, знак результата - в старшем разряде РОН R2.

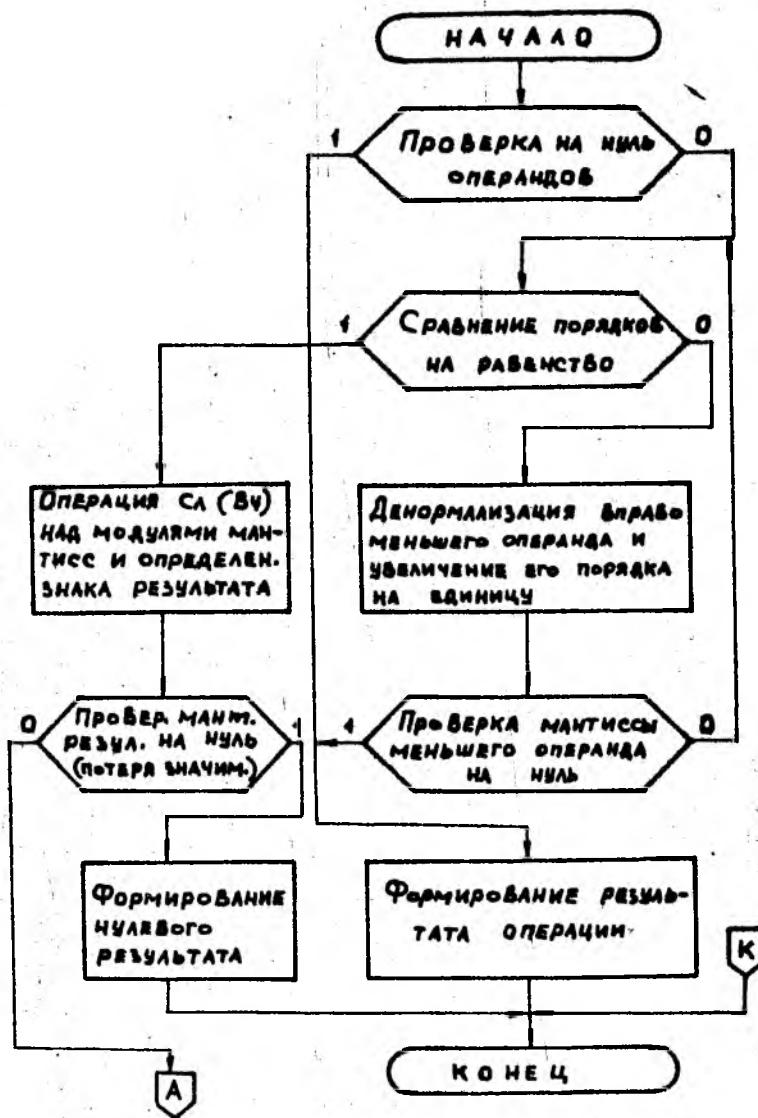

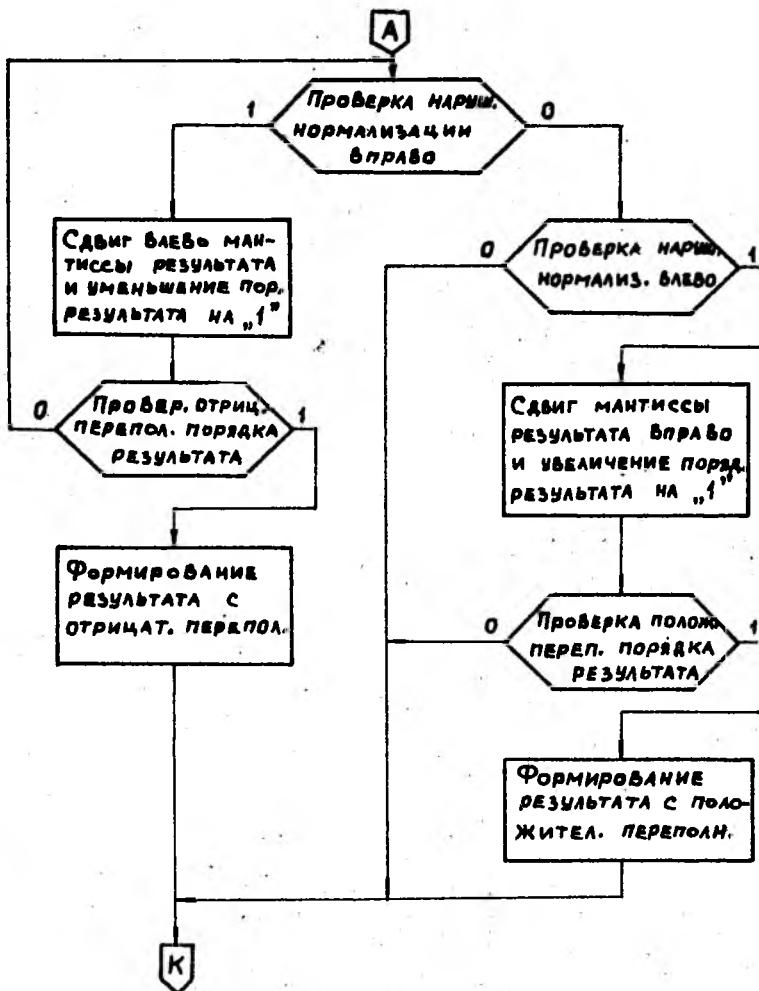

Укрупненная схема алгоритма операции показана на рис. 9. При реализации алгоритма будем предполагать, что нулевой операнд в МП представлен нулевыми кодами порядка и мантиссы. При возникновении переполнения порядка или потере значимости мантиссы результата ( $M_C = 0$ ) в поле порядка результата устанавливается код, содержащий единицы во всех разрядах. При этом согласно стандарту при положительном переполнении порядка результата во всех разрядах мантиссы результата устанавливаются единицы, а в знаковом разряде "0" (плюс), при отрицательном переполнении - единицы во всех разрядах мантиссы результата и "1" (минус) в знаковом разряде результата. Указанием на потерю значимости мантиссы результата служит отрицательность мантиссы с "0" во всех разрядах (с "1" во всех разрядах порядка результата). Запись констант в РОН МП осуществляется из соответствующего поля данных регистра микрокоманд (РМК).

Вариант задания выбирается в соответствии с табл. I4 - табл. I8.

Отчет должен содержать расчет разрядной сетки МП, детальную блок-схему заданного алгоритма, пример выполнения операции (типовых случаев) в заданном формате, структурную схему аппаратной части процессора с плавающей запятой (ПЗ), микроалгоритм операции (на уровне микроопераций над РОН МП), микропрограмму операции, описание построения микропрограммы и назначения полей микрокоманд,

Рис.9. Блок-схема алгоритма операции сложения (вычитания) чисел с плавающей запятой (начало)

Рис. 9. (окончание)

ТАБЛИЦА 14

| $d_1$ | ОПЕРАЦИЯ  | ОСНОВНЫЕ ИНТЕГРАЛ. СХЕМЫ        |

|-------|-----------|---------------------------------|

| 0     | СЛОЖЕНИЕ  |                                 |

| 1     | ВЫЧИТАНИЕ | ВС1, ВУ4, К1804ИР1,<br>К555КП12 |

ТАБЛИЦА 15

| $d_3$ | $d_2$ | ДИАПАЗОН ПРЕДСТАВЛЕНИЯ ЧИСЛА |

|-------|-------|------------------------------|

| 0     | 0     | $10^{\pm 18}$                |

| 0     | 1     | $10^{\pm 10}$                |

| 1     | 0     | $10^{\pm 30}$                |

| 1     | 1     | $10^{\pm 16}$                |

ТАБЛИЦА 16

| $d_3$ | $d_4$ | ТОЧНОСТЬ ПРЕСТАВЛЕНИЯ ЧИСЛА |

|-------|-------|-----------------------------|

| 0     | 0     | 7 ДЕСЯТИЧНЫХ ЦИФР           |

| 0     | 1     | $10^{—}$ — $10^{+}$         |

| 1     | 0     | $10^{—}$ — $10^{+}$         |

| 1     | 1     | $10^{—}$ — $10^{+}$         |

ТАБЛИЦА 17

| $d_7$ | $d_6$ | Способ представл. порядка                | ПРЕДСТАВ.<br>МАНТИССЫ |

|-------|-------|------------------------------------------|-----------------------|

| 0     | 0     | Дополнительный код                       | ПК                    |

| 0     | 1     | Смещенный код с положи-<br>тельным нулем | ПК                    |

| 1     | 0     | Смещенный код с отрица-<br>тельным нулем | ПК                    |

| 1     | 1     | Смещенный код с положи-<br>тельным нулем | ПК                    |

ТАБЛИЦА 18

| $d_8$ | $d_7$ | Основание характеристики |

|-------|-------|--------------------------|

| 0     | 0     | 2                        |

| 0     | 1     | 4                        |

| 1     | 0     | 16                       |

| 1     | 1     | 8                        |

расчет длительности такта МП.

При выборе формата данных и числа секций МП следует учитывать заданные диапазон и точность данных. Число [ ] цифровых разрядов порядка необходимо выбирать из соотношения  $10^k < 2^{2^m}$ , где  $m$  - число цифровых разрядов порядка при основании характеристики, равном 2;  $K$  - число [ ] цифровых разрядов порядка в десятичной системе. Кроме того, в формате данных необходимо предусмотреть разряд для хранения знака порядка. Количество цифровых разрядов мантиссы при основании характеристики, равном 2, выбирается из соотношения

$$10^{-\lambda} > 2^{-n},$$

где  $\lambda$  - число цифровых разрядов мантиссы в десятичной системе счисления;  $n$  - число цифровых разрядов в мантиссе двоичного кода (при основании характеристики, равном 2).

При других основаниях характеристики предыдущее выражение соответствующим образом корректируется. Полученное число разрядов окончательно округляется до целого количества тетрад (секций МП).

Пример выполнения типовых вариантов операции выполнить в соответствии с заданием и в выбранном формате.

Рассмотрим выполнение операции сложения чисел с плавающей запятой при основании характеристики 16 и смещенной характеристики с положительным нулем. При этом предположим, что формат данных имеет следующие поля: один байт используется для хранения знака мантиссы (1 бит) и характеристики (7 бит) и три байта (24 бит) для записи разрядов мантиссы. Пусть  $A = (-2485)_{16}$  и  $B = (423)_{16}$ . В нормализованной форме операнды имеют вид:  $A = (02485) \cdot 16^{+4}$ ,  $B = 0,423 \cdot 16^{-5}$ . В двоичном коде порядки равны:  $P_A = +100$ ,  $P_B = +11$ .

Смещенные характеристики с положительным нулем ( $E = 64$ ) будут равны:

$$P_A^{64} = 1000\ 000 + 100 = 1\ 000\ 100,$$

$$P_B^{64} = 1000\ 000 + 11 = 1000\ 011.$$

В целом числа в нормализованной форме будут иметь вид:

$$1.\ 1000\ 0100\ 0010\ 0100\ 1011\ 0101\ 0000\ 0000 \text{ (A)}$$

$$0.\ 1000\ 0011\ 0100\ 0010\ 0011\ 0000\ 0000\ 0000 \text{ (B)}.$$

Для сравнения характеристик операндов выполним вычитание характеристик:

$$\begin{array}{r} p_A^{64} = 1.000\ 0100 \\ + p_B^{64} = 0.111\ 1100 \\ +1 = 0.000\ 0001 \\ \hline (p_A - p_B)_{4K} = (1) 0.000\ 0001 \end{array}$$

разряда

"Знак" разности характеристик и перенос из знакового не совпадают, следовательно, переполнение сумматора характеристик отсутствует и на выходе сумматора имеем правильную разность порядков, которая равна +1. Следовательно, операнд В меньше А и мантисса В должна быть денормализована путем сдвига на один разряд вправо. После сдвига мантиссы В и увеличения порядка В на +1 получим:

$$0.1\ 000\ 0100' \ 0000\ 0100\ 0010\ 0011\ 0000\ 0000 \text{ (B).}$$

Выравнив порядки, складываем мантиссы А и В в дополнительном коде:

$$(M_A)_{4K} = 1.1101\ 1011\ 0100\ 1011\ 0000\ 0000$$

$$+ (M_B)_{4K} = 0.0000\ 0100\ 0010\ 0011\ 0000\ 0000$$

$$(M_A + M_B)_{4K} = (0)1.1101\ 1111\ 0110\ 1110\ 0000\ 0000.$$

Перенос в знаковый разряд и выходной перенос из знакового разряда не совпадают (0 и 1), поэтому переполнение сумматора мантиссы отсутствует. Мантисса результата получилась отрицательной, поэтому окончательно необходимо перейти к прямому коду:

$$(M_A + M_B)_{PK} = 1.0010\ 0000\ 1001\ 0010\ 0000\ 0000.$$

Таким образом, результат является нормализованным.

Следовательно, нормализованный результат сложения А и В равен:

$$1.1000\ 0100' \ 0010\ 0000\ 1001\ 0010\ 0000\ 0000.$$

В шестнадцатиричной системе результат равен:

$$(A + B)_{16} = (-0.2092) \cdot 16^{+4}.$$

Если сумма мантиссы после преобразования в прямой код является ненормализованной, на последнем этапе осуществляется нормализация результата.

Пусть, например, прямой код суммы мантисс и характеристики равны:

$$A+B = 1.1000\ 100' \ 0000\ 0101\ 0010\ 0000\ 0000\ 0000.$$

Нормализация результата сложения выполняется сдвигом мантиссы слева на один шестнадцатиричный разряд и вычитанием единицы из характеристики.

В результате сдвига мантиссы влево получим:

$$(M_{A+B})_{PK} = 1.0101\ 0010\ 0000\ 0000\ 0000\ 0000.$$

Уменьшим характеристику на единицу. Для этого характеристику суммируем с дополнением смещенный -1:

$$\begin{array}{r} P_{A+B}^{64} = 1.000\ 100' \\ + (-1)^{64} = 0.111\ 111' \end{array}$$

$$(P_{A+B}-1)_{4K} = (4)0.000\ 011'.$$

Результирующая характеристика +3 представлена в дополнительном коде. При этом переполнение сумматора порядков отсутствует, т.к.